# DS2251T 128k Soft Microcontroller Module

#### www.maxim-ic.com

#### **FEATURES**

#### 8051-Compatible Microcontroller Adapts to Its Task

32, 64, or 128kbytes of Nonvolatile SRAM for Program and/or Data Storage

In-System Programming via On-Chip Serial Port

Capable of Modifying its Own Program or Data Memory in the End System

Provides Separate Byte-Wide Bus for Peripherals

Performs CRC-16 Check of NV RAM Memory

#### High-Reliability Operation

Maintains All Nonvolatile Resources Up to 10 Years in the Absence of  $V_{CC}$  at Room Temperature

Power-Fail Reset

Early Warning Power-fail Interrupt

Watchdog Timer

Lithium Backed Memory Remembers System State

Precision Reference for Power Monitor

#### Fully 8051-Compatible

128 Bytes Scratchpad RAM Two Timer/Counters On-Chip Serial Port

32 Parallel I/O Port Pins

Permanently Powered Real-Time Clock

#### PIN CONFIGURATION

#### DESCRIPTION

The DS2251T 128k soft microcontroller module is an 8051-compatible microcontroller module based on nonvolatile RAM technology. It is designed for systems that need large quantities of nonvolatile memory. Like other members of the secure microcontroller family, it provides full compatibility with the 8051 instruction set, timers, serial port, and parallel I/O ports. By using NV RAM instead of ROM, the user can program, then reprogram the microcontroller while in-system. The application software can even change its own operation. This allows frequent software upgrades, adaptive programs, customized systems, etc. In addition, by using NV RAM, the DS2251T is ideal for data logging applications. The powerful real-time clock includes interrupts for time stamp and date. It keeps time to one-hundredth of seconds using its on-board 32kHz crystal.

1 of 22 REV: 061306

The DS2251T provides the benefits of NV RAM without using I/O resources. Between 32 kbytes and 128 kbytes of onboard NV RAM are available. A non-multiplexed Byte-wide address and data bus is used for memory access. This bus, which is available at the connector, can perform all memory access and also provide decoded chip enables for off-board memory mapped peripherals. This leaves the 32 I/O port pins free for application use.

The DS2251T provides high-reliability operation in portable systems or systems with unreliable power. These features include the ability to save the operating state, Power-fail Reset, Power-fail Interrupt, and Watchdog Timer. All nonvolatile memory and resources are maintained for over 10 years at room temperature in the absence of power.

A user loads programs into the DS2251T via its on-chip serial Bootstrap loader. This function supervises the loading of software into NV RAM, validates it, then becomes transparent to the user. Software is stored in onboard CMOS SRAM. Using its internal Partitioning, the DS2251T can divide a common RAM into user-selectable program and data segments. This Partition can be selected at program loading time, but can be modified anytime later. The microprocessor will decode memory access to the SRAM, access memory via its Byte-wide bus and write-protect the memory portion designated as program (ROM).

Operating information is contained in the Secure Microcontroller User's Guide. This data sheet provides ordering information, pinout, and electrical specifications.

#### ORDERING INFORMATION

| PART            | RAM SIZE (kB) | MAX CRYSTAL<br>SPEED (MHz) | TIMEKEEPING? |

|-----------------|---------------|----------------------------|--------------|

| DS2251T-32-16   | 32            | 16                         | Yes          |

| DS2251T-32-16#  | 32            | 16                         | Yes          |

| DS2251T-64-16   | 64            | 16                         | Yes          |

| DS2251T-64-16#  | 64            | 16                         | Yes          |

| DS2251T-128-16  | 128           | 16                         | Yes          |

| DS2251T-128-16# | 128           | 16                         | Yes          |

<sup>#</sup> Denotes a RoHS-compliant package that may contain lead exempt under the RoHS requirements.

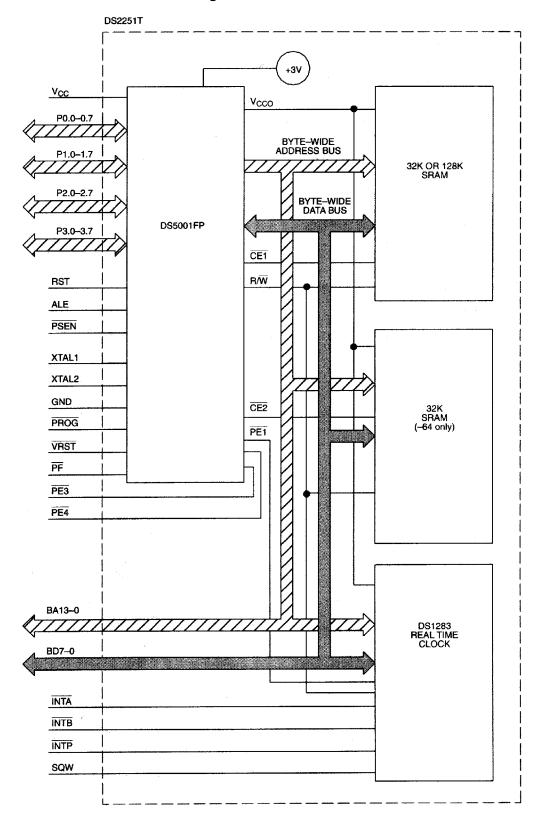

# **DS2251T BLOCK DIAGRAM** Figure 1

## **PIN ASSIGNMENT**

| PIN ASSIGNME |                       |  |  |  |  |  |  |

|--------------|-----------------------|--|--|--|--|--|--|

| PIN          | NAME                  |  |  |  |  |  |  |

| 1            | P1.0                  |  |  |  |  |  |  |

| 2            | P1.1                  |  |  |  |  |  |  |

| 3            | P1.2                  |  |  |  |  |  |  |

| 4            | P1.3                  |  |  |  |  |  |  |

| 5            | P1.4                  |  |  |  |  |  |  |

| 6            | P1.5                  |  |  |  |  |  |  |

| 7            | P1.6                  |  |  |  |  |  |  |

| 8            | P1.7                  |  |  |  |  |  |  |

| 9            | RST                   |  |  |  |  |  |  |

| 10           | P3.0/RXD              |  |  |  |  |  |  |

| 11           | P3.1/TXD              |  |  |  |  |  |  |

| 12           | P3.2/ <del>INT0</del> |  |  |  |  |  |  |

| 13           | P3.3/ <del>INT1</del> |  |  |  |  |  |  |

| 14           | P3.4/T0               |  |  |  |  |  |  |

| 15           | P3.5/T1               |  |  |  |  |  |  |

| 16           | P3.6/WR               |  |  |  |  |  |  |

| 17           | P3.7/RD               |  |  |  |  |  |  |

| 18           | XTAL1                 |  |  |  |  |  |  |

| PIN | NAME  |

|-----|-------|

| 19  | XTAL2 |

| 20  | GND   |

| 21  | P2.0  |

| 22  | P2.1  |

| 23  | P2.2  |

| 24  | P2.3  |

| 25  | P2.4  |

| 26  | P2.5  |

| 27  | P2.6  |

| 28  | P2.7  |

| 29  | PSEN  |

| 30  | ALE   |

| 31  | PROG  |

| 32  | P0.7  |

| 33  | P0.6  |

| 34  | P0.5  |

| 35  | P0.4  |

| 36  | P0.3  |

| PIN | NAME     |

|-----|----------|

| 37  | P0.2     |

| 38  | P0.1     |

| 39  | P0.0     |

| 40  | $V_{CC}$ |

| 41  | BA0      |

| 42  | BA1      |

| 43  | BA2      |

| 44  | BA3      |

| 45  | BA4      |

| 46  | BA5      |

| 47  | BA6      |

| 48  | BA7      |

| 49  | BA8      |

| 50  | BA9      |

| 51  | BA10     |

| 52  | BA11     |

| 53  | BA12     |

| 54  | BA13     |

| PIN | NAME             |

|-----|------------------|

| 55  | ĪNTB             |

| 56  | BD0              |

| 57  | BD1              |

| 58  | BD2              |

| 59  | BD3              |

| 60  | BD4              |

| 61  | BD5              |

| 62  | BD6              |

| 63  | BD7              |

| 64  | $R/\overline{W}$ |

| 65  | PF               |

| 66  | PE3              |

| 67  | PE4              |

| 68  | INTP             |

| 69  | ĪNTA             |

| 70  | SQW              |

| 71  | VRST             |

| 72  | BA15             |

## **PIN DESCRIPTION**

| PIN   | DESCRIPTION                                                                                                                                                                                                                                    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39–32 | <b>P0.0–P0.7.</b> General-purpose I/O Port 0. This port is open-drain and cannot drive a logic 1. It requires external pullups. Port 0 is also the multiplexed Expanded Address/Data bus. When used in this mode, it does not require pullups. |

| 1–8   | P1.0–P1.7. General-purpose I/O Port 1.                                                                                                                                                                                                         |

| 21–28 | <b>P2.0–P2.7.</b> General-purpose I/O Port 2. Also serves as the MSB of the Expanded Address bus.                                                                                                                                              |

| 10    | <b>P3.0/RXD.</b> General-purpose I/O port pin 3.0. Also serves as the receive signal for the onboard UART. This pin should <b>NOT</b> be connected directly to a PC COM port.                                                                  |

| 11    | <b>P3.1/TXD.</b> General-purpose I/O port pin 3.1. Also serves as the transmit signal for the onboard UART. This pin should <b>NOT</b> be connected directly to a PC COM port.                                                                 |

| 12    | P3.2/INTO. General-purpose I/O port pin 3.2. Also serves as the active low External Interrupt 0.                                                                                                                                               |

| 13    | P3.3/INT1. General-purpose I/O port pin 3.3. Also serves as the active low External Interrupt 1.                                                                                                                                               |

| 14    | <b>P3.4/T0.</b> General-purpose I/O port pin 3.4. Also serves as the Timer 0 input.                                                                                                                                                            |

| PIN    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                        |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | <b>P3.5/T1.</b> General-purpose I/O port pin 3.5. Also serves as the Timer 1 input.                                                                                                                                                                                                                                                                                                |

| 16     | P3.6/ WR. General-purpose I/O port pin. Also serves as the write strobe for Expanded bus operation.                                                                                                                                                                                                                                                                                |

| 17     | P3.7/RD. General-purpose I/O port pin. Also serves as the read strobe for Expanded bus operation.                                                                                                                                                                                                                                                                                  |

| 9      | <b>RST.</b> Active high reset input. A logic 1 applied to this pin will activate a reset state. This pin is pulled down internally, can be left unconnected if not used. An RC power-on reset circuit is not needed and is <b>NOT</b> recommended.                                                                                                                                 |

| 29     | <b>PSEN</b> . Program Store Enable. This active low signal is used to enable an external program memory when using the Expanded bus. It is normally an output and should be unconnected if not used.                                                                                                                                                                               |

| 30     | <b>ALE.</b> Address Latch Enable. Used to de-multiplex the multiplexed Expanded Address/Data bus on Port 0. This pin is normally connected to the clock input on a '373 type transparent latch.                                                                                                                                                                                    |

| 19, 18 | <b>XTAL2, XTAL1.</b> Used to connect an external crystal to the internal oscillator. XTAL1 is the input to an inverting amplifier and XTAL2 is the output.                                                                                                                                                                                                                         |

| 20     | GND. Logic ground.                                                                                                                                                                                                                                                                                                                                                                 |

| 40     | V <sub>CC</sub> . +5V                                                                                                                                                                                                                                                                                                                                                              |

| 72     | <b>BA15.</b> Monitor test point to reflect the logical value of A15. Not needed for memory access.                                                                                                                                                                                                                                                                                 |

| 54–41  | BA13–BA 0. Byte-wide Address bus bits 13–0. This bus is combined with the non-multiplexed data bus (BD7–BD0) to access onboard NV SRAM and off-board peripherals. Peripheral decoding is performed using PE3 and PE4. These are on 16k boundaries, so BA14 or BA15 are not needed. Read/write access is controlled by R/W. BA13–BA0 connect directly to memory-mapped peripherals. |

| 63–56  | <b>BD7–BD0.</b> Byte-wide Data Bus Bits 7–0. This 8-bit bi-directional bus is combined with the non-multiplexed address bus (BA14–BA0) to access on-board NV SRAM and off-board peripherals.                                                                                                                                                                                       |

| 64     | $R/\overline{w}$ . Read/Write. This signal provides the write enable to the SRAMs on the Byte-wide bus. It is controlled by the memory map and Partition. The blocks selected as Program (ROM) will be write-protected. This signal is also used for the write enable to off-board peripherals.                                                                                    |

| 66     | <b>PE3</b> . Peripheral Enable 3. Accesses data memory between addresses 8000h and BFFFh when the PES bit is set to a logic 1. PE3 is not lithium backed and can be connected to any type of peripheral function.                                                                                                                                                                  |

| 67     | <b>PE4</b> . Peripheral Enable 4. Accesses data memory between addresses C000h and FFFFh when the PES bit is set to a logic 1. PE4 is not lithium backed and can be connected to any type of peripheral function.                                                                                                                                                                  |

| 31     | <b>PROG</b> . Invokes the Bootstrap loader on a falling edge. This signal should be debounced so that only one edge is detected. If connected to ground, the micro will enter Bootstrap loading on power-up. This signal is pulled up internally.                                                                                                                                  |

| PIN | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71  | $\overline{\text{VRST}}$ . This I/O pin (open-drain with internal pullup) indicates that the power supply (V <sub>CC</sub> ) has fallen below the V <sub>CCMIN</sub> level and the micro is in a reset state. When this occurs, the DS2251T will drive this pin to a logic 0. Because the micro is lithium backed, this signal is guaranteed even when V <sub>CC</sub> = 0V. Because it is an I/O pin, it will also force a reset if pulled low externally. This allows multiple parts to synchronize their power-down resets. |

| 65  | $\overline{\text{PF}}$ . This output goes to a logic 0 to indicate that the micro has switched to lithium backup. It corresponds to $V_{CC} < V_{LI}$ . Because the micro is lithium backed, this signal is guaranteed even when $V_{CC} = 0V$ .                                                                                                                                                                                                                                                                               |

| 55  | INTB. INTB from the real-time clock. This output may be connected to a micro interrupt input.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 68  | INTP . INTP from the real-time clock. This open-drain output requires a pullup and may be connected to a micro interrupt input.                                                                                                                                                                                                                                                                                                                                                                                                |

| 69  | INTA. INTA from the real-time clock. This output may be connected to a micro interrupt input.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 70  | <b>SQW.</b> Square-wave output from the DS1283 real-time clock. Can be programmed to output a 1024Hz square wave.                                                                                                                                                                                                                                                                                                                                                                                                              |

#### INSTRUCTION SET

The DS2251T executes an instruction set that is object code compatible with the industry standard 8051 microcontroller. As a result, software development packages such as assemblers and compilers that have been written for the 8051 are compatible with the DS2251T.

A complete description of the instruction set and operation are provided in the Secure Microcontroller User's Guide

#### **MEMORY ORGANIZATION**

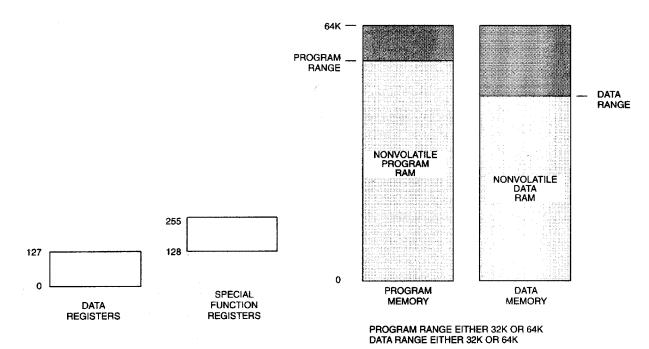

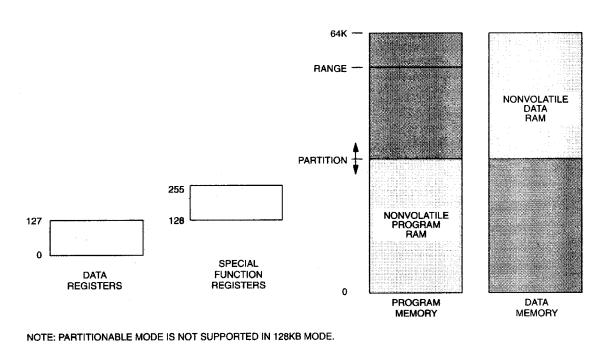

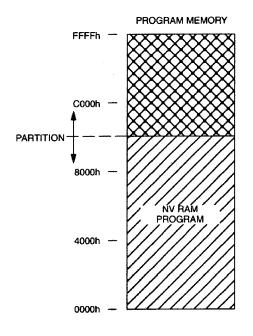

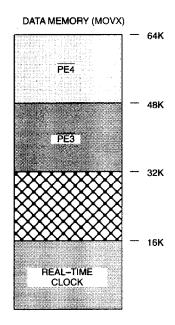

Figure 2 illustrates the memory map accessed by the DS2251T. The entire 64k of program and 64k of data are available to the byte-wide bus. This preserves the I/O ports for application use. The user controls the portion of memory that is actually mapped to the byte-wide bus by selecting the Program Range and Data Range. Any area not mapped into the NV RAM is reached via the Expanded bus on Ports 0 and 2. An alternate configuration allows dynamic Partitioning of a 64k space as shown in Figure 3. Selecting PES = 1 provides access to the real-time clock on the DS2251T and enables PE3 and PE4 for peripheral access as shown in Figure 4. These selections are made using Special Function Registers. The memory map and its controls are covered in detail in the Secure Microcontroller User's Guide.

# DS2251T MEMORY MAP IN NON-PARTITIONABLE MODE (PM = 1) Figure 2

# DS2251T MEMORY MAP IN PARTITIONABLE MODE (PM = 0) Figure 3

LEGEND:

= ON-CHIP REGISTERS

= ACCESSED VIA BYTEWIDE BUS

= ACCESSED VIA EXPANDED BUS

(PORTS 0 AND 2)

## DS2251T MEMORY MAP WITH (PES = 1) Figure 4

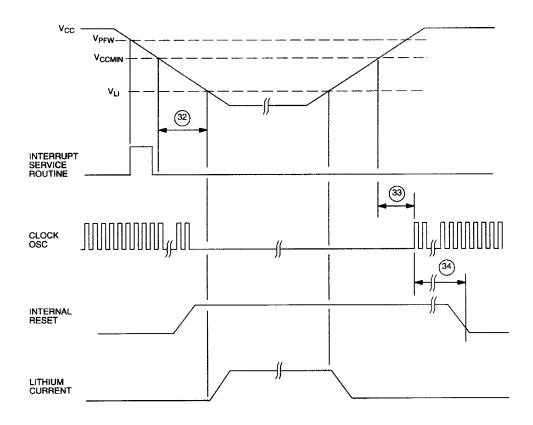

#### POWER MANAGEMENT

The DS2251T monitors  $V_{CC}$  to provide power-fail reset, early warning power-fail interrupt, and switchover to lithium backup. It uses an internal band-gap reference in determining the switch points. These are called  $V_{PFW}$ ,  $V_{CCMIN}$ , and  $V_{LI}$ , respectively. When  $V_{CC}$  drops below  $V_{PFW}$ , the DS2251T will perform an interrupt vector to location 2Bh if the power-fail warning is enabled. Full processor operation continues regardless. When power falls further to  $V_{CCMIN}$ , the DS2251T invokes a reset state. No further code execution will be performed unless power rises back above  $V_{CCMIN}$ . All decoded chip enables and the  $R/\overline{W}$  signal go to an inactive (logic 1) state. The  $\overline{VRST}$  signal will be driven to a logic 0.  $V_{CC}$  is still the power source at this time. When  $V_{CC}$  drops further to below  $V_{LI}$ , internal circuitry will switch to the built-in lithium cell for power. The majority of internal circuits will be disabled and the remaining nonvolatile states will be retained.  $\overline{PF}$  will be driven to a logic 0. The Secure Microcontroller User's Guide has more information on this topic. The trip points  $V_{CCMIN}$  and  $V_{PFW}$  are listed in the electrical specifications.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground         | 0.3V to $(V_{CC} + 0.5V)$ |

|-----------------------------------------------------|---------------------------|

| Voltage Range on V <sub>CC</sub> Relative to Ground | 0.3V to +6.0V             |

| Operating Temperature Range                         | 40°C to +85°C             |

| Storage Temperature (Note 1)                        |                           |

| Soldering Temperature                               | +260°C for 10 seconds     |

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

Note 1: Storage temperature is defined as the temperature of the device when  $V_{CC} = 0V$  and  $V_{LI} = 0V$ . In this state the contents of SRAM are not battery backed and are undefined.

#### DC CHARACTERISTICS

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                                                                                                                                              | SYMBOL               | MIN  | TYP  | MAX                  | UNITS | NOTES |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|------|----------------------|-------|-------|

| Input Low Voltage                                                                                                                                      | $V_{ m IL}$          | -0.3 |      | +0.8                 | V     | 1     |

| Input High Voltage                                                                                                                                     | $V_{\mathrm{IH1}}$   | 2.0  |      | V <sub>CC</sub> +0.3 | V     | 1     |

| Input High Voltage RST, XTAL1 PROG                                                                                                                     | $V_{IH2}$            | 3.5  |      | V <sub>CC</sub> +0.3 | V     | 1     |

| Output Low Voltage at $I_{OL} = 1.6 \text{mA}$ (Ports 1, 2, 3, $\overline{PF}$ )                                                                       | $V_{OL1}$            |      | 0.15 | 0.45                 | V     | 1, 7  |

| Output Low Voltage at $I_{OL}$ = 3.2mA (Ports 0, ALE, $\overline{PSEN}$ , BA13:BA0, BD7:BD0, R/ $\overline{W}$ , $\overline{PE3}$ : $\overline{PE4}$ ) | $V_{\mathrm{OL2}}$   |      | 0.15 | 0.45                 | V     | 1     |

| Output High Voltage<br>at $I_{OH} = -80\mu A$ (Ports 1, 2, 3)                                                                                          | $V_{\mathrm{OH1}}$   | 2.4  | 4.8  |                      | V     | 1     |

|                                                                                                                                                        | V <sub>OH2</sub>     | 2.4  | 4.8  |                      | V     | 1     |

| Input Low Current $V_{IN} = 0.45V \text{ (Ports 1, 2, 3)}$                                                                                             | $I_{IL}$             |      |      | -50                  | μΑ    |       |

| Transition Current; 1 to 0<br>$V_{IN} = 2.0V$ (Ports 1, 2, 3)                                                                                          | $I_{TL}$             |      |      | -500                 | μΑ    |       |

| Input Leakage Current 0.45 < V <sub>IN</sub> < V <sub>CC</sub> (Port 0)                                                                                | $I_{\rm IL}$         |      |      | ±10                  | μΑ    |       |

| RST Pulldown Resistor                                                                                                                                  | R <sub>RE</sub>      | 40   |      | 150                  | kΩ    |       |

| VRST Pullup Resistor                                                                                                                                   | $R_{VR}$             |      | 4.7  |                      | kΩ    |       |

| PROG Pullup Resistor                                                                                                                                   | $R_{PR}$             |      | 40   |                      | kΩ    |       |

| Power-Fail Warning Voltage                                                                                                                             | $V_{ m PFW}$         | 4.25 | 4.37 | 4.50                 | V     | 1     |

| Minimum Operating Voltage                                                                                                                              | V <sub>CC(MIN)</sub> | 4.00 | 4.12 | 4.25                 | V     | 1     |

| Operating Current at 16MHz                                                                                                                             | $I_{CC}$             |      |      | 45                   | mA    | 2     |

# **DC CHARACTERISTICS (continued)**

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                  |                 | SYMBOL            | MIN | TYP | MAX  | UNITS | NOTES |

|----------------------------|-----------------|-------------------|-----|-----|------|-------|-------|

| Idle Mode Current at 12MHz |                 | I <sub>IDLE</sub> |     |     | 7.0  | mA    | 3     |

| Stop Mode Current          |                 | $I_{STOP}$        |     |     | 80   | μΑ    | 4     |

| Pin Capacitance            |                 | $C_{IN}$          |     |     | 10   | pF    | 5     |

| Reset Trip Point in        | With BAT = 3.0V |                   | 4.0 |     | 4.25 | V     | 1     |

| Stop Mode                  | With BAT = 3.3V |                   | 4.4 |     | 4.65 | V     | 1     |

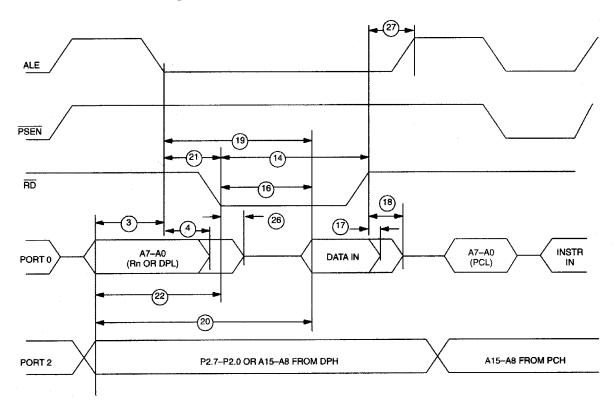

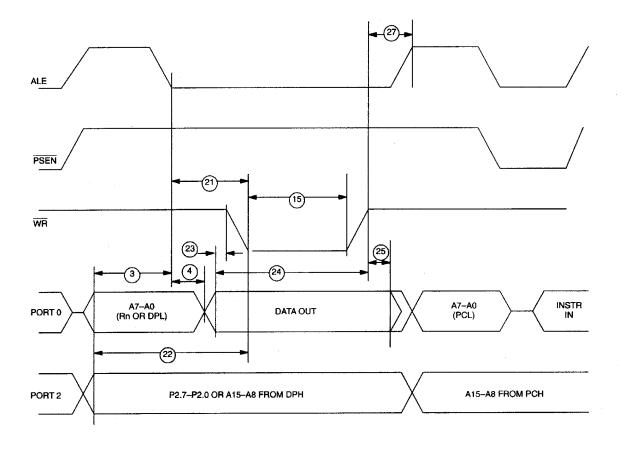

## AC CHARACTERISTICS—EXPANDED BUS MODE TIMING SPECIFICATIONS

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #   | PARAMETER                                |          | SYMBOL               | MIN                     | MAX                     | UNITS |  |

|-----|------------------------------------------|----------|----------------------|-------------------------|-------------------------|-------|--|

| 1   | Oscillator Frequency                     |          | $1/t_{\rm CLK}$      | 1.0                     | 16 (-16)                | MHz   |  |

| 2   | ALE Pulse Width                          |          | $t_{ m ALPW}$        | 2t <sub>CLK</sub> - 40  |                         | ns    |  |

| 3   | Address Valid to ALE Low                 |          | $t_{\mathrm{AVALL}}$ | t <sub>CLK</sub> - 40   |                         | ns    |  |

| 4   | Address Hold After ALE Low               |          | $t_{AVAAV}$          | t <sub>CLK</sub> - 35   |                         | ns    |  |

| 5   | ALE Low to Valid Instruction             | At 12MHz | +                    |                         | 4t <sub>CLK</sub> - 150 | ns    |  |

|     | In                                       | At 16MHz | t <sub>ALLVI</sub>   |                         | 4t <sub>CLK</sub> - 90  |       |  |

| 6   | ALE Low to PSEN Low                      |          | $t_{ALLPSL}$         | t <sub>CLK</sub> - 25   |                         | ns    |  |

| 7   | PSEN Pulse Width                         |          | $t_{\mathrm{PSPW}}$  | 3t <sub>CLK</sub> - 35  |                         | ns    |  |

| 8   | PSEN Low to Valid                        | At 12MHz | t                    |                         | 3t <sub>CLK</sub> - 150 | ng    |  |

| 0   | Instruction In                           | At 16MHz | t <sub>PSLVI</sub>   |                         | 3t <sub>CLK</sub> - 90  | ns    |  |

| 9   | Input Instr. Hold after PSEN Going High  |          | $t_{PSIV}$           | 0                       |                         | ns    |  |

| 10  | Input Instr. Float after PSEN Going High |          | $t_{PSIX}$           |                         | t <sub>CLK</sub> - 20   | ns    |  |

| 11  | Address Hold after PSEN Going High       |          | $t_{PSAV}$           | t <sub>CLK</sub> - 8    |                         | ns    |  |

| 12  | Address Valid to Valid                   | At 12MHz | +                    |                         | 5t <sub>CLK</sub> - 150 | ng    |  |

| 12  | Instruction In                           | At 16MHz | $t_{AVVI}$           |                         | 5t <sub>CLK</sub> - 90  | ns    |  |

| 13  | PSEN Low to Address Float                |          | $t_{PSLAZ}$          | 0                       |                         | ns    |  |

| 14  | RD Pulse Width                           |          | $t_{ m RDPW}$        | 6t <sub>CLK</sub> - 100 |                         | ns    |  |

| 15  | WR Pulse Width                           |          | $t_{\mathrm{WRPW}}$  | 6t <sub>CLK</sub> - 100 |                         | ns    |  |

| 1.6 | DD I t- W-1: 1 D-t- I                    | At 12MHz | 4                    |                         | 5t <sub>CLK</sub> - 165 |       |  |

| 16  | RD Low to Valid Data In                  | At 16MHz | $t_{ m RDLDV}$       |                         | 5t <sub>CLK</sub> - 105 | ns    |  |

| 17  | Data Hold after RD High                  |          | $t_{ m RDHDV}$       | 0                       |                         | ns    |  |

| 18  | Data Float after RD High                 |          | t <sub>RDHDZ</sub>   |                         | 2t <sub>CLK</sub> - 70  | ns    |  |

| 19  | ALE Low to Valid Data In At 12MHz        |          | t <sub>ALLVD</sub>   |                         | 8 <sub>CLK</sub> - 150  | ns    |  |

|     |                                          |          | •                    | i                       |                         |       |  |

# AC CHARACTERISTICS—EXPANDED BUS MODE TIMING SPECIFICATIONS (continued)

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #  | PARAMETER                    | SYMBOL   | MIN                  | MAX                     | UNITS                   |             |

|----|------------------------------|----------|----------------------|-------------------------|-------------------------|-------------|

| 19 | ALE Low to Valid Data In     | At 12MHz | 4                    |                         | 8 <sub>CLK</sub> - 150  | nc          |

| 19 | ALE LOW to Valid Data III    | At 16MHz | $t_{ m ALLVD}$       |                         | 8t <sub>CLK</sub> - 90  | ns          |

| 20 | Valid Address to Valid Data  | At 12MHz | <b>t</b>             |                         | 9t <sub>CLK</sub> - 165 | ng          |

| 20 | In                           | At 16MHz | $t_{ m AVDV}$        |                         | 9t <sub>CLK</sub> - 105 | ns          |

| 21 | ALE Low to RD or WR Low      |          | $t_{ m ALLRDL}$      | 3t <sub>CLK</sub> -50   | $3t_{CLK} + 50$         | ns          |

| 22 | Address Valid to RD or WR Lo | )W       | $t_{AVRDL}$          | 4t <sub>CLK</sub> -130  |                         | ns          |

| 23 | Data Valid to WR Going Low   |          | $t_{\mathrm{DVWRL}}$ | t <sub>CLK</sub> - 60   |                         | ns          |

| 24 | Data Valid to ym High        | At 12MHz | 4                    | 7t <sub>CLK</sub> - 150 |                         | <b>19</b> G |

| 24 | Data Valid to WR High        | At 16MHz | $t_{ m DVWRH}$       | 7t <sub>CLK</sub> - 90  |                         | ns          |

| 25 | Data Valid after WR High     |          | $t_{\mathrm{WRHDV}}$ | t <sub>CLK</sub> - 50   |                         | ns          |

| 26 | RD Low to Address Float      |          | $t_{RDLAZ}$          |                         | 0                       | ns          |

| 27 | RD or WR High to ALE High    |          | t <sub>RDHALH</sub>  | t <sub>CLK</sub> - 40   | $t_{\rm CLK} + 50$      | ns          |

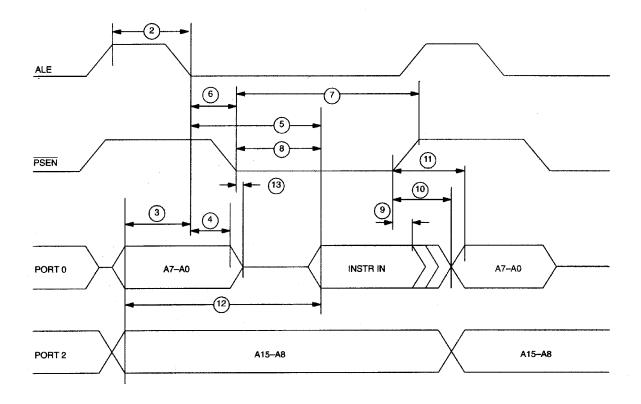

## **EXPANDED PROGRAM MEMORY READ CYCLE**

# **EXPANDED DATA MEMORY READ CYCLE**

# **EXPANDED DATA MEMORY WRITE CYCLE**

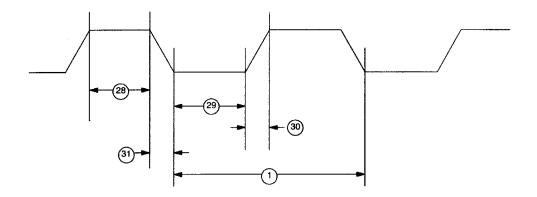

# AC CHARACTERISTICS—EXTERNAL CLOCK DRIVE

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| 1 00 1 11 |                          |          |                     |     |     |       |

|-----------|--------------------------|----------|---------------------|-----|-----|-------|

| #         | PARAMETER                |          | SYMBOL              | MIN | MAX | UNITS |

|           |                          | At 12MHz |                     | 20  |     |       |

| 28        | External Clock High Time | At 16MHz | t <sub>CLKHPW</sub> | 15  |     | ns    |

| 20        | External Clock Low Time  | At 12MHz | 4                   | 20  |     | ***   |

| 29        | External Clock Low Time  | At 16MHz | $t_{ m CLKLPW}$     | 15  |     | ns    |

| 20        | External Clock Rise Time | At 12MHz | t <sub>CLKR</sub>   |     | 20  | ***   |

| 30        | External Clock Rise Time | At 16MHz |                     |     | 15  | ns    |

| 31        | External Clock Fall Time | At 12MHz | ,                   |     | 20  | 4.5   |

|           |                          | At 16MHz | $t_{ m CLKF}$       |     | 15  | ns    |

|           |                          |          |                     |     |     |       |

# **EXTERNAL CLOCK TIMING**

## **AC CHARACTERISTICS—POWER CYCLE TIMING**

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #  | PARAMETER                                 | SYMBOL     | MIN | MAX      | UNITS     |

|----|-------------------------------------------|------------|-----|----------|-----------|

| 32 | Slew Rate from V <sub>CCMIN</sub> to 3.3V | $t_{ m F}$ | 130 |          | μs        |

| 33 | Crystal Startup Time                      | $t_{CSU}$  |     | (Note 6) |           |

| 34 | Power-On Reset Delay                      | $t_{POR}$  |     | 21,504   | $t_{CLK}$ |

## **POWER CYCLE TIMING**

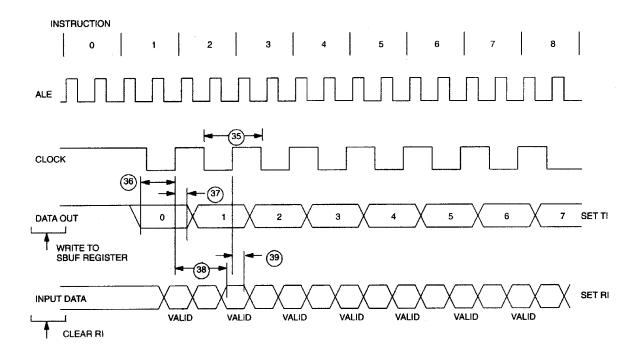

## **AC CHARACTERISTICS—SERIAL PORT TIMING: MODE 0**

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #  | PARAMETER                                | SYMBOL               | MIN                      | MAX                      | UNITS |

|----|------------------------------------------|----------------------|--------------------------|--------------------------|-------|

| 35 | Serial Port Cycle Time                   | $t_{\mathrm{SPCLK}}$ | $12t_{CLK}$              |                          | μs    |

| 36 | Output Data Setup to Rising Clock Edge   | $t_{DOCH}$           | 10t <sub>CLK</sub> - 133 |                          | ns    |

| 37 | Output Data Hold after Rising Clock Edge | $t_{CHDO}$           | 2t <sub>CLK</sub> - 117  |                          | ns    |

| 38 | Clock Rising Edge to Input Data Valid    | $t_{CHDV}$           |                          | 10t <sub>CLK</sub> - 133 | ns    |

| 39 | Input Data Hold after Rising Clock Edge  | $t_{ m CHDIV}$       | 0                        |                          | ns    |

## **SERIAL PORT TIMING: MODE 0**

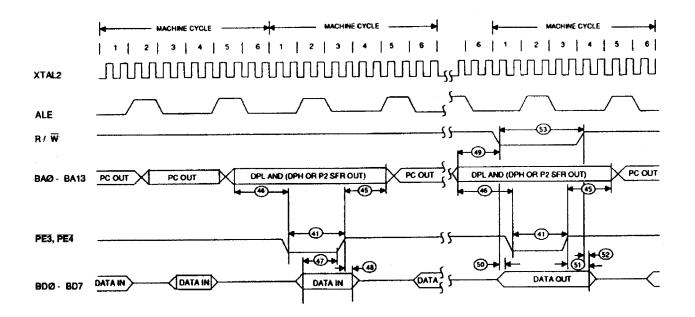

## AC CHARACTERISTICS—PARALLEL PROGRAM LOAD TIMING

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #  | PARAMETER                                                              | SYMBOL             | MIN                    | MAX | UNITS |

|----|------------------------------------------------------------------------|--------------------|------------------------|-----|-------|

| 41 | Pulse Width of PE 3-4                                                  | $t_{CEPW}$         | 4t <sub>CLK</sub> - 35 |     | ns    |

| 45 | Byte-wide Address Hold after $\overline{PE}$ 3-4 High During MOVX      | t <sub>CEHDA</sub> | 4t <sub>CLK</sub> - 30 |     | ns    |

| 46 | Delay from Byte-wide Address Valid $\overline{PE}$ 3-4 Low During MOVX | t <sub>CELDA</sub> | 4t <sub>CLK</sub> - 35 |     | ns    |

| 47 | Byte-wide Data Setup to $\overline{PE}$ 3-4 High During MOVX (read)    | t <sub>DACEH</sub> | $1t_{\text{CLK}} + 40$ |     | ns    |

| 48 | Byte-wide Data Hold after PE 3-4 High<br>During MOVX (read)            | $t_{CEHDV}$        | 10                     |     | ns    |

| 49 | Byte-wide Address Valid to R/W Active During MOVX (write)              | $t_{ m AVRWL}$     | 3t <sub>CLK</sub> - 35 |     | ns    |

| 50 | Delay from R/W Low to Valid Data Out During MOVX (write)               | $t_{RWLDV}$        | 20                     |     | ns    |

| 51 | Valid Data Out Hold Time from PE 3-4 High                              | $t_{CEHDV}$        | 1t <sub>CLK</sub> - 15 |     | ns    |

| 52 | Valid Data Out Hold Time from R/W High                                 | $t_{RWHDV}$        | 0                      |     | ns    |

| 53 | Write Pulse Width (R/W Low Time)                                       | $t_{RWLPW}$        | 6t <sub>CLK</sub> - 20 |     | ns    |

## **BYTE-WIDE BUS TIMING**

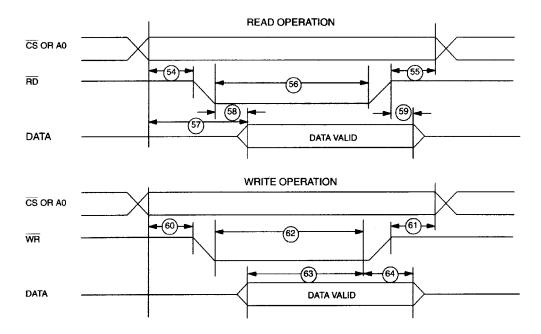

#### RPC AC CHARACTERISTICS—DBB READ

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #  | PARAMETER                                                        | SYMBOL            | MIN | MAX | UNITS |

|----|------------------------------------------------------------------|-------------------|-----|-----|-------|

| 54 | $\overline{\text{CS}}$ , $A_0$ Setup to $\overline{\text{RD}}$   | $t_{AR}$          | 0   |     | ns    |

| 55 | $\overline{\text{CS}}$ , $A_0$ Hold After $\overline{\text{RD}}$ | $t_{RA}$          | 0   |     | ns    |

| 56 | RD Pulse Width                                                   | $t_{RR}$          | 160 |     | ns    |

| 57 | $\overline{\text{CS}}$ , $A_0$ to Data Out Delay                 | $t_{\mathrm{AD}}$ |     | 130 | ns    |

| 58 | RD to Data Out Delay                                             | $t_{RD}$          | 0   | 130 | ns    |

| 59 | RD to Data Float Delay                                           | $t_{RDZ}$         |     | 85  | ns    |

#### RPC AC CHARACTERISTICS—DBB WRITE

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #   | PARAMETER                                                      | SYMBOL            | MIN | MAX | UNITS |

|-----|----------------------------------------------------------------|-------------------|-----|-----|-------|

| 60  | $\overline{\text{CS}}$ , $A_0$ Setup to $\overline{\text{WR}}$ | $t_{ m AW}$       | 0   |     | ns    |

| 61A | $\overline{\text{CS}}$ , Hold After $\overline{\text{WR}}$     | $t_{WA}$          | 0   |     | ns    |

| 61B | A <sub>0</sub> , Hold After WR                                 | $t_{WA}$          | 20  |     | ns    |

| 62  | WR Pulse Width                                                 | $t_{ m WW}$       | 20  |     | ns    |

| 63  | Data Setup to WR                                               | $t_{\mathrm{DW}}$ | 130 |     | ns    |

| 64  | Data Hold After WR                                             | $t_{\mathrm{WD}}$ | 20  |     | ns    |

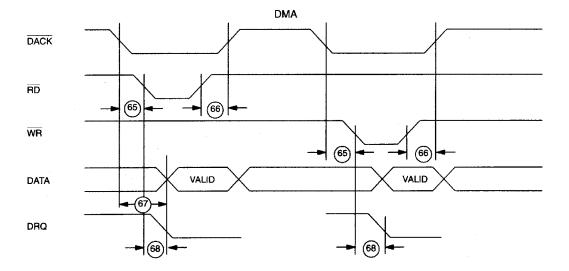

### **AC CHARACTERISTICS—DMA**

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #  | PARAMETER               | SYMBOL    | MIN | MAX | UNITS |

|----|-------------------------|-----------|-----|-----|-------|

| 65 | DACK to WR or RD        | $t_{ACC}$ | 0   |     | ns    |

| 66 | RD or WR to DACK        | $t_{CAC}$ | 0   |     | ns    |

| 67 | DACK to Data Valid      | $t_{ACD}$ | 0   | 130 | ns    |

| 68 | RD or WR to DRQ Cleared | $t_{CRQ}$ |     | 110 | ns    |

# AC CHARACTERISTICS—PROG

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #  | PARAMETER             | SYMBOL    | MIN | MAX | UNITS |

|----|-----------------------|-----------|-----|-----|-------|

| 69 | PROG Low to Active    | $t_{PRA}$ | 48  |     | CLKS  |

| 70 | PROG High to Inactive | $t_{PRI}$ | 48  |     | CLKS  |

## **RPC TIMING MODE 16**

# **RPC TIMING MODE 16 (continued)**

#### **NOTES:**

- 1. All voltages are referenced to ground.

- 2. Maximum operating  $I_{CC}$  is measured with all output pins disconnected; XTAL1 driven with  $t_{CLKR}$ ,  $t_{CLKF}$ =10ns,  $V_{IL}$  = 0.5V; XTAL2 disconnected; RST = PORT0 =  $V_{CC}$ .

- 3. Idle mode  $I_{IDLE}$  is measured with all output pins disconnected; XTAL1 driven with  $t_{CLKR}$ ,  $t_{CLKF} = 10$ ns,  $V_{IL} = 0.5$ V; XTAL2 disconnected; PORT0 =  $V_{CC}$ , RST =  $V_{SS}$ .

- 4. Stop mode  $I_{STOP}$  is measured with all output pins disconnected; PORT0 =  $V_{CC}$ ; XTAL2 not connected; RST = XTAL1 =  $V_{SS}$ .

- 5. Pin capacitance is measured with a test frequency—1MHz,  $T_A = +25$ °C.

- 6. Crystal startup time is the time required to get the mass of the crystal into vibrational motion from the time that power is first applied to the circuit until the first clock pulse is produced by the on-chip oscillator. The user should check with the crystal vendor for a worst-case specification on this time.

- 7.  $\overline{PF}$  pin operation is specified with  $V_{BAT} \ge 3.0 V$ .

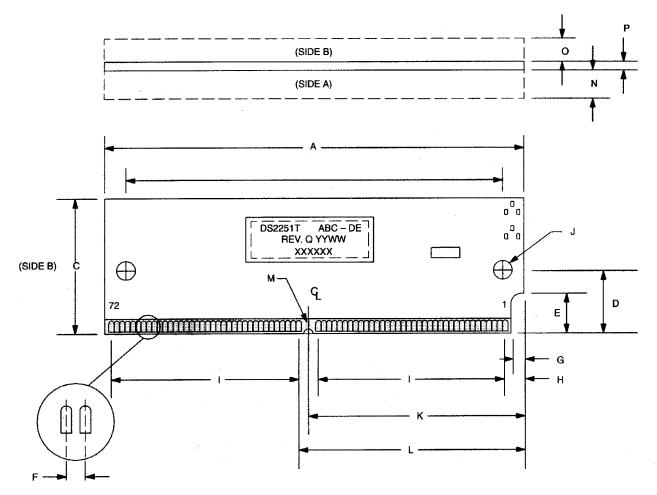

# **PACKAGE DRAWING**

| PKG | INC   | HES   |

|-----|-------|-------|

| DIM | MIN   | MAX   |

| Α   | 4.245 | 4.255 |

| В   | 3.979 | 3.989 |

| С   | 0.995 | 1.005 |

| D   | 0.395 | 0.405 |

| E   | 0.245 | 0.255 |

| F   | 0.050 | BSC   |

| G   | 0.075 | 0.085 |

| Н   | 0.245 | 0.255 |

| I   | 1.750 | BSC   |

| J   | 0.120 | 0.130 |

| K   | 2.120 | 2.130 |

| L   | 2.245 | 2.255 |

| М   | 0.057 | 0.067 |

| N   | -     | 0.275 |

| 0   | -     | 0.145 |

| Р   | 0.047 | 0.054 |

#### DATA SHEET REVISION SUMMARY

The following represent the key differences between 12/13/95 and 08/13/96 version of the DS2251T data sheet. Please review this summary carefully.

- 1. Change V<sub>CC</sub> slew rate definition to reference 3.3V instead of V<sub>LI</sub>.

- 2. Add minimum value to PCB thickness.

The following represent the key differences between 08/15/96 and 05/29/97 version of the DS2251T data sheet. Please review this summary carefully.

1.  $\overline{PF}$  signal moved from  $V_{OL2}$  test specification to  $V_{OL1}$ . (PCND73001)

The following represent the key differences between 05/28/97 and 11/08/99 version of the DS2251T data sheet. Please review this summary carefully. (PCN I80903)

- 1. Correct Absolute Maximum Ratings to reflect changes to DS5001FP microprocessor.

- 2. Add note clarifying that SRAM contents are not defined under storage temperature conditions.

The following represent the key differences between 11/08/99 and 01/18/00 version of the DS2251T data sheet. Please review this summary carefully.

1. Document converted from interleaf to Microsoft Word.

The following represent the key differences between 01/18/00 and 06/13/06 version of the DS2251T data sheet. Please review this summary carefully.

- 1. Updated reference in Features (High-Reliability Operation) to 10-year NV RAM data life to include room temperature caveat.

- 2. Added RoHS-compliant packages to Ordering Information table.

- 3. Replaced references to "Secure Microcontroller Data Book" with "Secure Microcontroller User's Guide."